SuVolta e Fujitsu Semiconductor hanno annunciato una nuova tecnologia basata sui transistor a basso consumo definita dalle due aziende deeply depleted channel (DDC) ideata per ridurre i consumi di ben l’80% rispetto ai chip disponibili attualmente sul mercato.

Per ridurre i consumi è necessaria una tensione inferiore, con un processo di produzione inferiore ai 20 nanometri è possibile ottenere processori a basso consumo, questo è quanto ha dichiarato il presidente e capo del settore tecnologico di SuVolta, Bruce McWilliams. Entrambe le aziende, hanno realizzato con successo blocchi SRAM da 576 kb a 65 nanometri in grado di funzionare con soli 0,425 volt.

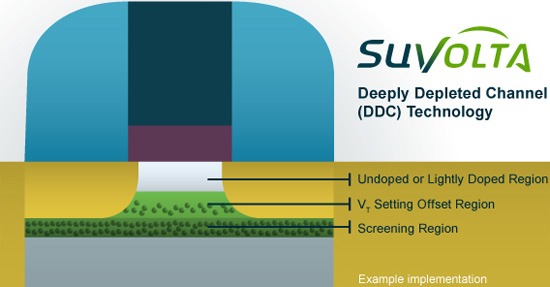

Sono state in grado di ottenere un calo del 50%, rispetto alle soluzioni attuali senza intaccare le frequenze. Il DDC di Suvolta, riduce le variabilità della tensione di soglia e permette di continuare lo scaling con soluzioni CMOS, il tutto funziona formando un DDC in presenza di una tensione che successivamente viene applicata al gate. In altre parole, tale implementazione prevede che il DDC abbia diverse regioni, una non dopata e l’altra leggermente dopata in modo da compensare la tensione di soglia con una screening.

La prima regione rimuove i dopanti che permettono la creazione di un canale impoverito in questo modo viene migliorata la mobilità per avere una maggiore efficacia della corrente, riducendo l’RDF si ottengono tecnologie ETSOI e FINfet più complesse di quelle attuali. Per quanto riguarda invece la seconda regione, protegge la carica e imposta la profondità dello strato impoverito.

Rispetto ai transistor di Intel, la differenza è che quest’ultimo necessita di una medesima tensione mentre con quelli di Suvolta può essere modificata.